thiết kế vi mạch số với hdl

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (5.74 MB, 36 trang )

<span class="text_page_counter">Trang 1</span><div class="page_container" data-page="1">

<b>KHOA ĐIỆN ĐIỆN TỬ</b>

<b>---THIẾT KẾ VI MẠCH SỐ VỚI HDL</b>

<b>Biên soạn: Đỗ Hồng ThắngSinh viên khóa K21</b>

</div><span class="text_page_counter">Trang 2</span><div class="page_container" data-page="2">Như vậy con chip này có sức chứa 16 transistor (kích thước)

Do số lượng transistor trong một con chip đơn đã tăng theo số hàm mũ. Một con chip Si ngày nay chứa tới hàng trăm ngàn hay hàng trăm triệu con transistor bây giờ lên tới hàng tỉ con transistor.

Trong quá khứ, chức năng chính của phần cứng số là các hệ thống tính tốn. Khi mà, con chip nhỏ hơn, nhanh hơn, rẻ hơn và nhiều khả năng hơn,…Nhiều hệ thống điện tử, điều khiển, truyền thông và hệ thống cơ điện tử đã được số hóa bên trong, sử dụng các mạch điện số lưu trữ dữ liệu, xử lý dữ liệu hoặc truyền thông tin.

Khi mà ứng dụng trở nên lớn hơn phức tạp hơn, thì các cơng việc thiết kế mạch số trở nên khó hơn. Phát triển và sản suất 1 mạch số là quá trình là rất phức tạp.

<b>2. Các công nghệ thiết bị</b>

Nếu chúng ta muốn xây dựng hệ thống số theo yêu cầu của khách hàng thì có rất nhiều dạng cơng nghệ khác nhau để mà lựa chọn.

Khơng có cơng nghệ nào tốt nhất.

Chúng ta phải xem xét mối tương quan giữa các hệ số khác nhau, các hệ số đó bao gồm: tài nguyên, tốc độ, khả năng và giá thành của con chip.

<b>2.1. Chế tạo vi mạch</b>

Một con vi mạch được tạo ra bởi nhiều lớp: Si pha tạp, tinh thể Si, kim loại và oxit Si, được xây dựng trên lớp đầu, trên wafer Si mỏng.

</div><span class="text_page_counter">Trang 3</span><div class="page_container" data-page="3">Một vài lớp dùng để tạo nên transistor, và những lớp còn lại người ta dùng làm dây dẫn kết nối.

<b>2.2. Phân loại các công nghệ thiết bị</b>

Chúng ta cần phải hiểu rõ sự khác biệt giữa 2 công nghệ ASIC (Application Specific Integrated Circuit) và non-ASIC.

Chúng ta có thể chia các cơng nghệ ra thành các dạng như sau: Full-custom ASIC (Công nghệ ASIC đặt chế hồn tồn) Standard-cell ASIC (Cơng nghệ ASIC tế bào chuẩn) Gate array ASIC (Công nghệ ASIC mảng, cổng, chuỗi)

Complex field-programmable logic device (Các thiết bị logic có thể lập trình theo trường phức tạp)

Simple field-programmable logic device (Các thiết bị logic có thể lập trình theo trường đơn giản)

</div><span class="text_page_counter">Trang 4</span><div class="page_container" data-page="4"><b>2.2.1. Full-custom ASIC</b>

Chúng ta phải đều khiển toàn bộ mạch điện và thạm chí cách bố trí thủ cơng vị trí của từng con transistor để mà nó có thể tương thích với các yêu cầu về hiệu suất hoặc yêu cầu về tài nguyên đặt biệt.

Mạch sau khi thiết kế thì được tối ưu hồn tồn và có một hiệu suất tốt nhất có thể. Thật khơng may, thiết kế một cái mạch điện ở cấp độ trans cực kỳ phức tạp và nó chỉ phù hợp với mạch điện có kích cỡ nhỏ.

Sẽ khơng thực tế nếu chúng ta sử dụng cái phương pháp thiết kế này để đi thiết kế toàn bộ hệ thống, mà hệ thống ngày nay có thể chứa lên đến 10 hoặc 100 triệu trans.

Một CPU năm 1971 chỉ có 2.300 trans thì hiện nay (2016) đã có tới 7.2 tỉ trans với 22 nhân nhờ q trình sản xuất 14nm (dịng 22-core Xeon Broadwell-E5).

<b>Ứng dụng chính: dùng để thiết kế ra các thành phần logic cơ bản (cổng AND, OR,</b>

NOT). Chúng có thể sử dụng như là các khối xây dựng của một hệ thống lớn.

<b>Ứng dụng khác: thiết kế các mạch điện dạng bit như là mạch nhớ 1-bit, mạch cộng</b>

<b>2.2.2. Standard-cell ASIC</b>

Một mạch điện được xây dựng bằng cách sử dụng một chuỗi hoặc là tập hợp các thành phần logic đã được xác định trước, và được gọi là <b>các tế bào chuẩn</b>.

</div><span class="text_page_counter">Trang 5</span><div class="page_container" data-page="5">Các tế bào này đã được thiết kế trước và bố trí của chúng đã có hiệu lực và đã kiểm tra rồi.

Cơng nghệ này cho phép chúng ta làm việc ở cấp độ cổng hơn là cấp độ dùng trans và do đó nó làm đơn giản đi một cách đáng kể cái quá trình thiết kế.

Các nhà thiết kế thiết bị thường cung cấp các thư viện của tế bào chuẩn như là các khối xây dựng cơ bản.

Các thư viện đó thường chứa các cổng logic cơ bản: Các thành phần kết hợp đơn giản, chẳng hạn như:

Cổng AND, OR, NOT.

Trong công nghệ này mạch điện được tạo ra từ các tế bào.

Các loại tế bào và kết nối bên trong thì phụ thuộc vào các ứng dụng độc lập. Trong khi bố trí của tế bào đã được xác định, thì bố trí của tồn bộ mạch điện là duy nhất và do đó việc chế tạo 1 chip theo công nghệ tế bào chuẩn gần giống như là chế tạo chip của full-custom ASIC, và tất cả lớp được chúng ta tùy chỉnh hết.

<b>2.2.3. Gate array ASIC</b>

Trong công nghệ này, một mạch được xây dựng từ một mảng các ô được xác định

</div><span class="text_page_counter">Trang 6</span><div class="page_container" data-page="6">Chip mảng cổng chỉ bao gồm một loại tế bào, được gọi là<b> tế bào cơ bản</b>. Tế bào cơ bản khá đơn giản, giống như một cổng logic.

Các tế bào cơ bản này được sắp xếp trước và đặt ở những vị trí cố định, được căn chỉnh dưới dạng mảng một hoặc hai chiều.

Vì vị trí và loại được xác định trước, nên các tế bào cơ bản có thể được chế tạo sẵn. Việc tùy chỉnh mạch được thực hiện bằng cách chỉ định kết nối giữa các tế bào này. Các nhà chế tạo của công nghệ này cũng cung cấp những thư viện của các thành phần đã được thiết kế, như là các tế bào macro.

Chúng được xây dựng từ các tế bào cơ bản.

Các tế bào macro sẽ có những kết nối bên trong được xác định và cung cấp cho người thiết kế nhiều khối logic phức tạp hơn.

<b>So sánh công nghệ tế bào chuẩn:</b>

Việc chế tạo thiết bị mảng cổng đơn giản hơn nhiều do cấu trúc mảng cố định của nó.

Vì mảng là chung cho tất cả các ứng dụng nên tế bào có thể được chế tạo trước. Trong quá trình xây dựng chip, chỉ các lớp mặt nạ ngoài kim loại, chỉ định kết

nối, là duy nhất cho một ứng dụng và do đó phải được tùy chỉnh.

Điều này làm giảm số lớp tùy chỉnh từ 10-15 lớp xuống còn 3-5 lớp và đơn giản hóa đáng kể quy trình chế tạo.

<b>2.2.4. Complex field-programmable logic device</b>

Bây giờ chúng tôi kiểm tra một số công nghệ không phải ASIC.

Công nghệ không phải ASIC linh hoạt nhất là thiết bị lập trình trường phức tạp (CFPD). Trong công nghệ này, một thiết bị bao gồm một dãy các tế bào logic tổng quát và cấu trúc kết nối tổng quát. Mặc dù các tế bào logic và cấu trúc kết nối được đúc sẵn nhưng cả hai đều có thể lập trình được.

Khả năng lập trình có được bằng cách sử dụng "cầu chì" hoặc "cơng tắc" bán dẫn mà có thể được thiết lập là hở mạch hoặc ngắn mạch.

</div><span class="text_page_counter">Trang 7</span><div class="page_container" data-page="7">Việc tùy chỉnh được thực hiện bằng cách định cấu hình thiết bị với mẫu cầu chì cụ thể. Quá trình này có thể được thực hiện bởi một lập trình viên thiết bị đơn giản, rẻ tiền.

Các cấu trúc cơ bản của mảng cổng ASIC và CFPD có phần giống nhau.

Tuy nhiên, cấu trúc kết nối của CFPD được xác định trước và do đó có nhiều ràng buộc hơn đối với định tuyến tín hiệu. Để giảm số lượng kết nối, nhiều chức năng hơn được tích hợp vào các tế bào logic của CFPD, làm cho tế bào logic phức tạp hơn nhiều so với tế bào cơ bản hoặc tế bào tiêu chuẩn của ASIC. Theo độ phức tạp và cấu trúc của các tế bào logic, CFPD có thể được chia thành hai loại chính: CPLD (Complex programmable logic device), FPGA (Field programmable gate array).

<b>2.2.4.1. Công nghệ CPLD (có trước FPGA)</b>

Các tế bào logic của các thiết bị CPLD khá phức tạp so với FPGA.

Nó thường chứa 1 loại flip-flop D và 1 đơn vị giống như PAL với cấu hình các thành phần tích. Cấu trúc nối dây của thiết bị CPLD có khuynh hướng tập trung hơn, với nhiều nhóm dây định tuyến tập trung.

</div><span class="text_page_counter">Trang 8</span><div class="page_container" data-page="8"><b>2.2.4.2. Cơng nghệ FPGA (có sau CPLD)</b>

Ngược lại với CPLD, thì tế bào logic của thiết bị FPGA thường nhỏ hơn.

Nó cũng chứa 1 flip-flop D và 1 bảng tra nhỏ hoặc là tập hợp các mạch đa hợp. Cấu trúc nối dây bên trong giữa các tế bào có khuynh hướng phân tán và linh hoạt hơn. Do tính chất phân phối của nó, FPGA phù hợp hơn với các thiết bị lập trình trường phức tạp lớn, công suất cao.

<b>2.2.5. Simple field-programmable logic device (có trước CN4)</b>

SFPLD là các thiết bị với cấu trúc bên trong khá đơn giản.

Các thiết bị này thường được gọi là các thiết bị logic có thể lập trình (PLD). SFPD thường được xây dựng như là mảng 2 cấp, với mảng cổng AND và OR. Nối dây bên trong của 1 hoặc 2 mảng có thể lập trình được để tạo ra một hàm logic được biểu diễn dưới dạng tổng của các tích.

</div><span class="text_page_counter">Trang 9</span><div class="page_container" data-page="9"><b>Các thiết bị này bao gồm:</b>

Programmable read only memory (PROM), với mảng cổng OR cho phép chúng ta lập trình.

Programmable array logic (PAL), với cổng AND có phép chúng ta lập trình. Programmable logic array (PLA), cho phép cả 2 mảng đều có thể lập trình.

<b>Khơng giống như thiết bị FPGA và CPLD.</b>

SFPLD khơng có cấu trúc nối dây bên trong tổng quát, do đó chức năng của nó bị hạn chế một cách đáng kể. ROM, PAL và PLA ngày nay được xem như là các thành phần bên trong của các thiết bị ASIC hoặc CPLD hơn là sử dụng nó một cách độc lập.

<b>2.2.6. Off-the-shelf small and medium-scaled IC (SSI/MSI) components.</b>

Trước khi xuất hiện các thiết bị có thể lập trình theo vùng, chỉ có một giải pháp duy nhất là dùng các thành phần vi mạch tích hợp cỡ nhỏ/cỡ trung để đi thiết kế mạch. Các thành phần này là các mạch điện nhỏ các phần nhỏ, với chức năng giới hạn và cố định.

<b>Ví dụ về họ TTL 7400</b>

Khi chúng ta thiết kế một hệ thống số phải thiết kế từ dưới lên, chúng ta sẽ xây dựng mạch điện dần từ các thành phần nhỏ hơn.

<b>Nhược điểm chính của phương pháp này là hầu hết các nguồn tài nguyên như là:</b>

công suất, chuyển tiếp chuyển bo, giá thành sản suất,…được tính bởi một gói và nó khơng phải là thành phần Si. Xa hơn nữa, khơng có phần mềm tổng hợp nào mà có thể thiết kế mạch sử dụng cơng nghệ cỡ nhỏ/cỡ trung như thế này, và như thế chúng ta không thể tự động. Khi các thiết bị có thể lập trình trở nên nhiều chức năng hơn và giá thành thấp hơn, thì việc thiết kế một hệ thống số theo yêu cầu của khách hàng và chính vì thế nó khơng được xem xét trong tài liệu này.

</div><span class="text_page_counter">Trang 10</span><div class="page_container" data-page="10"><b>CHƯƠNG 2: TỔNG QUAN VỀ NGƠN NGỮ HDL (3)</b>

<b>1. Ngơn ngữ mơ tả phần cứng</b>

<b>1.1. Hạn chế của ngơn ngữ lập trình truyền thống</b>

Có nhiều loại ngơn ngữ lập trình máy tính, từ Fortran đến C đến Java. Thật không may, chúng không đủ để mơ hình hóa phần cứng kỹ thuật số. Hầu hết các ngơn ngữ lập trình mục đích chung truyền thống, chẳng hạn như C, được mơ hình hóa sau một quy trình tuần tự. Trong quá trình này, các thao tác được thực hiện theo thứ tự tuần tự, mỗi lần một thao tác.

Mặt khác, đặc điểm của phần cứng kỹ thuật số rất khác so với mơ hình tuần tự. Một hệ thống kỹ thuật số điển hình thường được xây dựng bởi các bộ phận nhỏ hơn, với hệ thống dây tùy chỉnh kết nối các cổng đầu vào và đầu ra của các bộ phận này.

Khi tín hiệu thay đổi, các bộ phận được kết nối với tín hiệu sẽ được kích hoạt và một loạt các hoạt động mới được bắt đầu tương ứng. Các thao tác này được thực hiện đồng thời và mỗi thao tác sẽ mất một khoảng thời gian cụ thể, thể hiện độ trễ lan truyền của một bộ phận cụ thể, để hoàn thành. Sau khi hoàn thành, mỗi phần cập nhật giá trị của cổng xuất tương ứng.

<b>1.2. Sử dụng chương trình HDL</b>

Mơ hình tuần tự được sử dụng trong các ngơn ngữ lập trình truyền thống khơng thể nắm bắt được các đặc tính song song của phần cứng số. Cần có các ngơn ngữ đặc biệt (nghĩa là HDL) được thiết kế để mơ hình hóa phần cứng kỹ thuật số.

VHDL và Verilog là hai HDL được sử dụng rộng rãi nhất.

</div><span class="text_page_counter">Trang 11</span><div class="page_container" data-page="11">VHDL là viết tắt của VHSIC (Very High Speed Integrated Circuit) HDL.

Sự phát triển của VHDL ban đầu được tài trợ bởi Bộ Quốc phòng Hoa Kỳ như một tiêu chuẩn tài liệu phần cứng vào đầu những năm 1980.

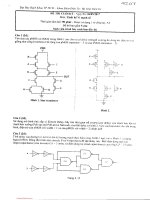

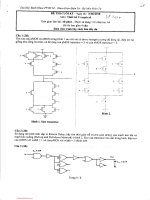

<b>2. Khái niệm VHDL cơ bản thơng qua ví dụVí dụ: Mạch phát hiện chẵn lẻ.</b>

Có một đầu ra, chẵn và ba đầu vào, a(2), a(1) và a(0), được nhóm thành một bus.

<b>2.1. Mơ tả tổng qt</b>

Mã bao gồm hai đơn vị chính: <b>entity declaration</b> và <b>architecture body.</b>

<b> Entity declaration: (Khai báo tín hiệu vào ra của mạch điện đang mô tả)</b>

</div><span class="text_page_counter">Trang 12</span><div class="page_container" data-page="12"><b> Architecture body: Phần thân kiến trúc chỉ định hoạt động bên trong hoặc tổ</b>

chức của một mạch.

<b>Dòng tiếp theo là khai báo tín hiệu:</b>

Khối xây dựng cơ bản bên trong thân kiến trúc là một lệnh đồng thời.

Lệnh đồng thời.

Tín hiệu hoặc port bên trái là ngõ ra và tất cả tín hiệu và các port xuất hiện trong biểu thức bên phải là tín hiệu ngõ vào.

Phần thân kiến trúc này bao gồm năm câu lệnh đồng thời. Mà có thể được hiểu là một tập hợp của năm phần mạch.

<b>Lưu ý rằng, thứ tự của các câu lệnh đồng thời này không quan trọng.</b>

</div><span class="text_page_counter">Trang 13</span><div class="page_container" data-page="13"><b>Ví dụ: chúng ta có thể sắp xếp lại mã như sau</b>

<b>Cách khác: sử dụng thao tác xor và biểu thức có thể được viết là</b>

Sơ đồ khái niệm:

<b>2.2. Mô tả cấu trúc</b>

Trong cách mô tả cấu trúc, một mạch được xây dựng từ các bộ phận nhỏ hơn. Mô tả chỉ định loại bộ phận nào được sử dụng và cách các bộ phận này được

kết nối.

Mô tả về cơ bản là một sơ đồ, đại diện cho một sơ đồ khối hoặc sơ đồ mạch điện.

</div><span class="text_page_counter">Trang 20</span><div class="page_container" data-page="20">Khi một chương trình được xử lý, nó được chia thành các đơn vị thiết kế riêng lẻ và mỗi đơn vị được phân tích và lưu trữ độc lập.

Có 5 loại đơn vị thiết kế: Entity declaration Architecture body

Package declaration (khai báo gói) Package body (thân gói) Configuration (cấu hình)

Một gói VHDL thường chứa một tập hợp các mục thường được sử dụng, chẳng hạn như kiểu dữ liệu, chương trình con và các thành phần, cần thiết cho nhiều chương trình VHDL.

Như tên gợi ý, một khai báo gói bao gồm khai báo các mục này.

Phần thân gói thường chứa phần triển khai và mã của các chương trình con. Trong VHDL, nhiều thân kiến trúc có thể được liên kết với một khai báo entity. Một cấu hình chỉ định phần thân kiến trúc nào sẽ được liên kết với phần khai báo entity.

<b>3. Các yếu tố từ vựng và định dạng chương trình3.1. Yếu tố từ vựng</b>

Các yếu tố từ vựng là các đơn vị cú pháp cơ bản trong một chương trình VHDL. Chúng bao gồm chú thích, đặt tên, các từ khóa, con số, các ký tự và chuỗi.

<b>Chú thích:</b>

Một nhận xét bắt đầu bằng hai dấu gạch ngang, --, theo sau là nội dung nhận xét. Mọi thứ sau biểu tượng -- trong dòng sẽ bị bỏ qua.

Nhận xét chỉ dành cho mục đích tài liệu và khơng ảnh hưởng đến mã.

<b>VD: chúng tôi đã thêm nhận xét vào mã VHDL trước đó:</b>

<b>Đặt tên:</b>

Định danh là tên của một đối tượng trong VHDL. Các quy tắc cơ bản để tạo thành một định danh là:

</div><span class="text_page_counter">Trang 21</span><div class="page_container" data-page="21"> Mã định danh chỉ có thể chứa các chữ cái, chữ số thập phân và dấu gạch dưới.

Ký tự đầu tiên phải là một chữ cái.

Ký tự cuối cùng không được là dấu gạch dưới. Hai dấu gạch dưới liên tiếp không được phép.

<b>VD: các số nhận dạng sau là hợp lệ:</b>

A10, next_state, NextState, mem_addr_enable

Mặt khác, các định danh sau vi phạm một trong các quy tắc và sẽ gây ra lỗi cú pháp: Sig#3, -X10, 7segment, X10_, hi_there

Vì VHDL khơng phân biệt chữ hoa chữ thường nên các mã định danh sau đây như là

Chúng tôi cũng có thể thêm một dấu gạch dưới để tăng cường khả năng đọc.

<b>VD: 12_3456 giống với 123456 và 2#0011_1010_1101# giống với</b>

<b>4. Các đối tượng VHDL4.1. SIGNAL</b>

Signal là đối tượng phổ biến nhất và chúng tơi đã sử dụng nó trong các ví dụ trước. Một tín hiệu phải được khai báo trong phần khai báo của phần thân kiến trúc.

Cú pháp khai báo tín hiệu được đơn giản hóa là

<b>VD: dịng sau khai báo các tín hiệu a, b và c với kiểu dữ liệu std_logic:</b>

Theo định nghĩa của VHDL, chúng ta có thể chỉ định một giá trị ban đầu tùy chọn trong phần khai báo tín hiệu. <b>VD</b>: chúng ta có thể gán giá trị ban đầu là '0' cho các tín hiệu trước đó:

</div><span class="text_page_counter">Trang 22</span><div class="page_container" data-page="22">Biến là một khái niệm được tìm thấy trong ngơn ngữ lập trình truyền thống. Nó có thể được coi là một "vị trí bộ nhớ tượng trưng" nơi một giá trị có thể được lưu trữ và sửa đổi. Khơng có ánh xạ trực tiếp giữa một biến và một phần cứng. Một biến chỉ có thể được khai báo và sử dụng trong một quy trình và là cục bộ của quy trình đó.

<b>Ứng dụng chính của một biến là mơ tả hành vi trừu tượng của một hệ thống.</b>

Cú pháp khai báo biến tương tự như khai báo tín hiệu: Cú pháp đơn giản hóa của phép gán biến là

<b>5. Các loại dữ liệu và các toán tử5.1. Các kiểu dữ liệu của VHDL</b>

Trong VHDL, mỗi đối tượng có một kiểu dữ liệu. Một kiểu dữ liệu được xác định bởi:

Một tập hợp các giá trị mà một đối tượng có thể đảm nhận.

Một tập hợp các hoạt động có thể được thực hiện trên các đối tượng của kiểu dữ liệu này.

Integer:

VHDL không xác định phạm vi chính xác của kiểu số nguyên nhưng xác định rằng phạm vi tối thiểu là từ (-2 ) đến (2 -1), tương ứng với 32 bit.<small>3131</small>

Boolean: được định nghĩa là (sai, đúng). Bit: được định nghĩa là (‘0’, ‘1’).

Bit_vector: được định nghĩa là mảng một chiều với các phần tử thuộc kiểu dữ liệu bit.

</div>